Omega Vehicle Security DAQ-16 User Manual

Page 19

When configured for a 48-bit divider, the first sampling period will be slightly longer than

the others because the first clock period is required to load the initial value of the

multi-function timer. The following equation calculates the additional time of the first period:

t

= 100ns * [N1 * N2]

add

To minimize the amount of additional time required for the first sample, select clock dividers

such that N1 and N2 are as small as possible and N3 is as large as possible. Using the

equations above, the minimum and maximum data sampling rates and the amount of

additional time required for the first sample can be calculated.

Maximum sampling rate:

Minimum sampling rate:

N1 = 2, N2 = 2, N3 = 25

N1 = 65535, N2 = 65535, N3 = 65535

t = 100 x 10 * [(2)*(2)*(25)]

t = 100 x 10 * [(65535)*(65535)*(65535)]

−

9

−

9

t = 100 x 10 * 100

t = 100 x 10 * [2.815 x 10 ]

−

9

−

9

14

t = 10 us

t = 28.146 x 10 sec

6

f = 10 x 10 / [(2)*(2)*(25)]

t = 325 days, 18 hours, 23 minutes, 29 sec

6

f = 10 x 10 / 100

f = 10 x 10 / [(65535)*(65535)*(65535 )]

6

6

f = 100 Khz

f = 10 x 10 / [2.815 x 10 ]

6

14

f = 35.529 nHz

t

= 100 x 10 * [2 * 2]

t

= 100 x 10 * [65535 * 65535]

add

−

9

add

−

9

t

= 100 x 10 * 4

t

= 100 x 10 * [4.295 x 10 ]

add

−

9

add

−

9

9

t

= 400 ns

t

= 429.5 sec

add

add

2.5.2

External Clock

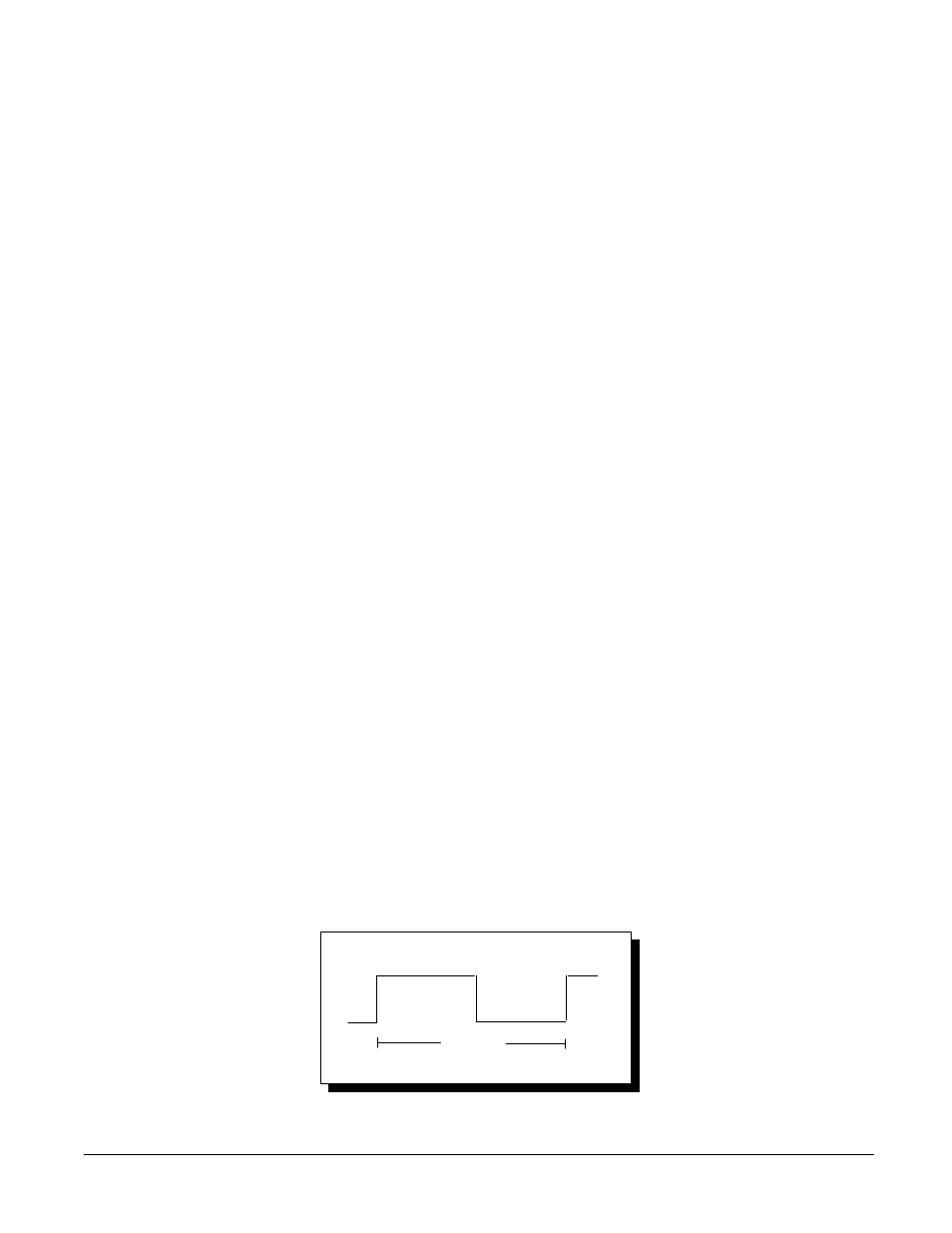

The external clock input to the DAQ-16 is a TTL level (0 - 5 volt) signal. This input may be

used to control the sampling rate directly, or it may be fed through a pre-divider (the

multi-function timer) with the timer output controlling the A/D sampling rate. When used to

control the sampling rate directly, the frequency of the external clock input may be varied

from DC to 100 KHz as long as the width of the low and high portions of the clock are a

minimum of 1 us each. The A/D conversion cycle will begin on each rising edge of the

external clock input. (See Figure 2-7).

10 usec

min

1 usec min 1 usec min

Figure 2-7. Sampling Rate External Clock Pulses

DAQ-16 Users Manual 19