1 block diagram - radio frequency (rf), 1 general rf indications, Receiver – Sony CMD-J5/J16 User Manual

Page 17: Transmitter

17

SECTION 6

DIAGRAMS

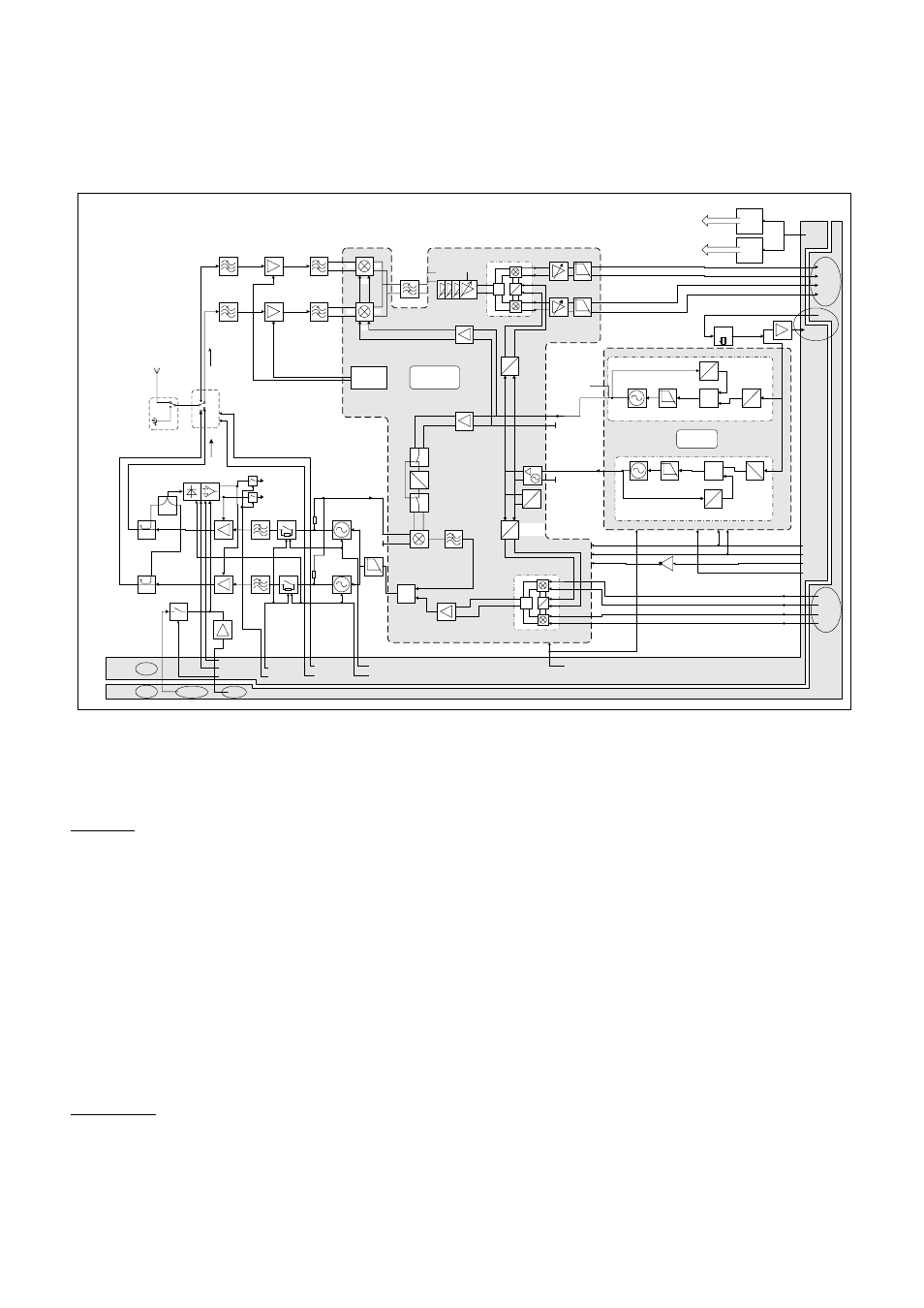

6.1 Block Diagram - Radio Frequency (RF)

6.1.1 General RF Indications

The radio part of the CMD-J5/J16 handles the air interface according to the GSM specifications.

It is the main contributor for the dualband functionality for E-GSM 900 and DCS 1800.

Receiver

The receiver consists of two separated RF paths for GSM and DCS 1800 each.

On the transmission line between the antenna switch of the RF part and the antenna there is the RF connector

including a mechanical switch to connect an external antenna for accessory use. The integrated mechanical

switch switches between the helix antenna and the external RF antenna connection. As long as a plug is

connected the antenna is deactivated and all RF signals go across the connector.

The GMSK (Gaussian-filtered minimum shift keying) modulated 900 MHz / 1800 MHz signal received by the

antenna is filtered, gained and downconverted into the baseband via an intermediate frequency of 440 MHz.

The 440 MHz filter is followed by a tuneable amplifier and IQ demodulator. Behind the demodulator there are

additional base band amplifiers and low pass filters.

The In Phase (I) and Quadrature (Q) signal outputs are balanced each.

A 13 MHz voltage-controlled-temperature-compensated crystal oscillator (VCTCXO) generates the clock

frequency for the PLL and baseband part.

Transmitter

In the transmit direction the digitally GMSK-modulated baseband signal is upconverted to the transmit frequency

in the 900 MHz / 1800 MHz band via an intermediate frequency of 195 MHz (GSM) / 325 MHz (DCS 1800) by

means of an IQ modulator and the subsequenting sum loop.

All RF and IQ signals are balanced signals in order to suppress crosstalk effects. According to GSM

recommendations transmitter and receiver are never active at the same time.

(TDMA system “Time Division Multiple Access”).

2

1

ϕ

3/5

1

ϕ

M

1

ϕ

N

1

N

1

LO2 (IF) PLL

1 MHz step

N

N+1

1

LO1 (RF) PLL

200 kHz step

PLL

Antenna

RF Connector with

mechanical switch

13 MHz

Transceiver

90°

0

°

∑

2

1

VCTCXO

LO1 (RF) PLL:

- RX -

GSM 1365..1400 MHz

DCS 1365..1440 MHz

- TX -

GSM 1370..1440 MHz

DCS 1385..1460 MHz

LO1

VCO

RX

TX

GSM

880..915 MHz

DCS1800

1710..1785 MHz

Loop

Filter

DCS

GSM

Ceramic Filter

1805..1880 MHz

SAW Filter

925..960 MHz

LNA

LNA

SAW Filter

1805..1880 MHz

IF

SAW Filter

440 MHz

LO2 (IF) PLL

RX 880 MHz

TX 975 MHz

GSM :5

DCS :3

GSM 195 MHz

DCS 325 MHz

RF

RF

IF

IF

LO

LO

Q

I

90°

0

°

∑

Q

I

LP Filter

PA

RX:

GSM 1365..1400 MHz

DCS 1365..1440 MHz

88

0 M

H

z

440 MHz

TX:

GSM 1370..1440 MHz

DCS 1385..1460 MHz

Tx GSM VCO

880..915 MHz

Tx DCS VCO

1710..1785 MHz

Detector and

Level control

TX:

GSM 685..720 MHz

DCS 1385..1460 MHz

Antenna

Switch

LO2

VCO

5

1

GSM

DCS

SAW Filter

925..960 MHz

Total VCO Range:

1365 to 1460 MHz

PA

Loop

Filter

Loop

Filter

Pin diode

switch

SERCK

SERDA

SERLE1

SERLE2

RF_IC_EN

TX_SW_EN

GSM_VCO_EN

DCS_VCO_EN

GSM_TX_EN

DCS_TX_EN

DET_EN

RF_EN

TXP

CLK13M

AFC

LNA Bias

control

VCC_RF

LDO

VCC_SYNTH

LDO

DET_TX

Pin diode

switch

TXIP

TXIN

TXQP

TXQN

RXIP

RXIN

RXQP

RXQN

97

5 M

H

z

IQ Demodulator

Rx frontend filter

Rx interstage filter

Sum loop

IF Amplifier (PGC)

APC loop

Directional

coupler + LPF

Directional

coupler

Phase

detector

Down

Converter

LP Filter

1st Rx mixer

BB amplifier and

low pass filter

IC 1

IC 2

Total VCO Range:

880 to 975 MHz

AUX_DAC

LP Filter

TXP_OFS_EN

APC_DOWN

Analog

signals

Digital

signals