Maxq family user’s guide: maxq2000 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2000 Supplement User Manual

Page 15

MAXQ Family User’s Guide:

MAXQ2000 Supplement

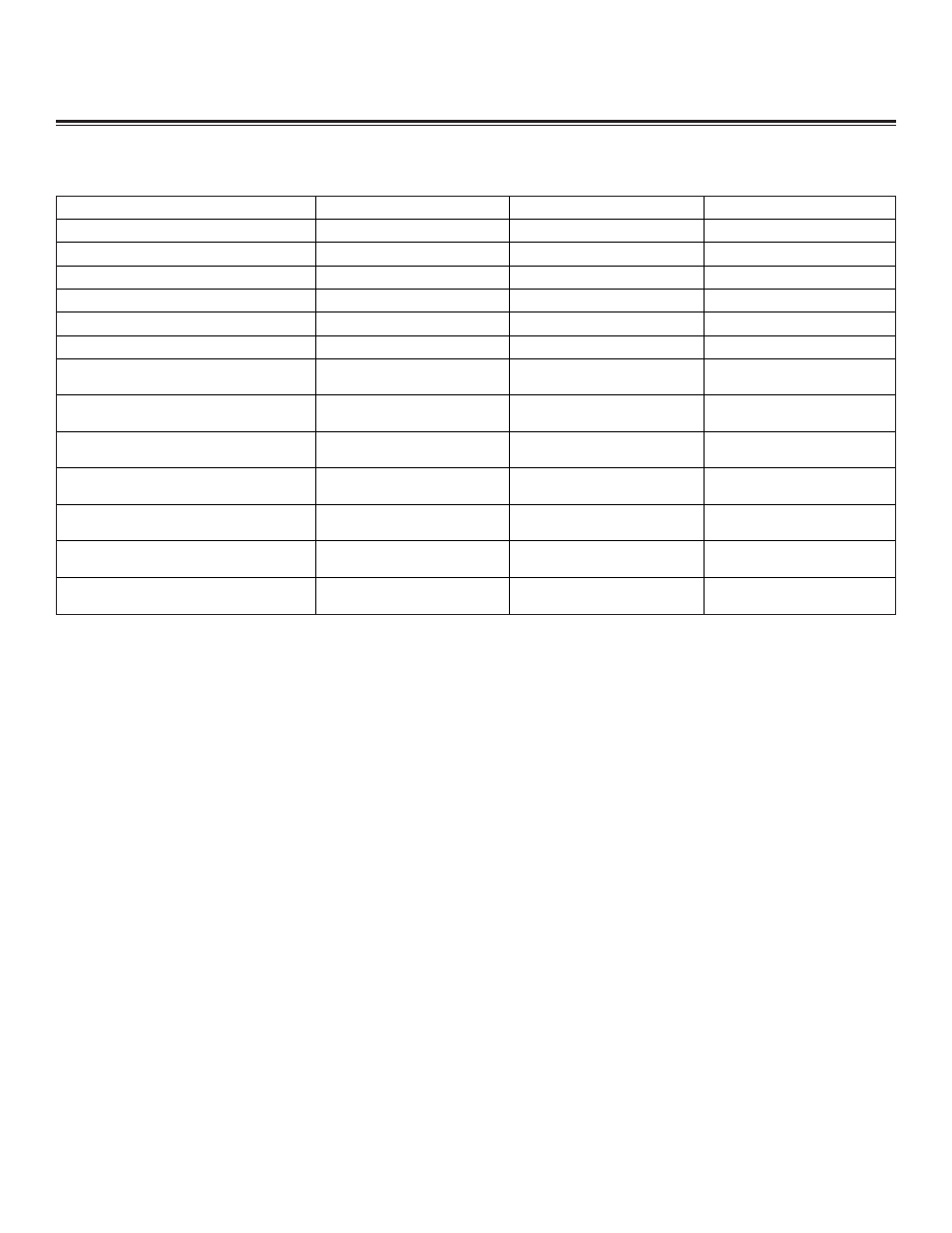

Table 2. MAXQ2000 Interrupt Sources and Control Bits (continued)

INTERRUPT

MODULE ENABLE BIT

LOCAL ENABLE BIT

INTERRUPT FLAG

Timer 1–Capture/Compare

IM4 (IMR.4)

ET2 (T2CNA1.7)

TCC2 (T2CNB1.1)

Timer 1–Overflow

IM4 (IMR.4)

ET2 (T2CNA1.7)

TF2 (T2CNB1.3)

Timer 2–Low Compare

IM4 (IMR.4)

ET2L (T2CNB2.7)

T2CL (T2CNB2.0)

Timer 2–Low Overflow

IM4 (IMR.4)

ET2L (T2CNB2.7)

TF2L (T2CNB2.2)

Timer 2–Capture/Compare

IM4 (IMR.4)

ET2 (T2CNA2.7)

TCC2 (T2CNB2.1)

Timer 2–Overflow

IM4 (IMR.4)

ET2 (T2CNA2.7)

TF2 (T2CNB2.3)

1-Wire Presence Detect*

IM3 (IMR.3);

EOWMI (OWD[5].7)

EPD (OWD[3].0)

PD (OWD[2].0)

1-Wire Transmit Buffer Empty*

IM3 (IMR.3);

EOWMI (OWD[5].7)

ETBE (OWD[3].2)

TBE (OWD[2].2)

1-Wire Transmit Shift Register Empty*

IM3 (IMR.3);

EOWMI (OWD[5].7)

ETMT (OWD[3].3)

TEMT (OWD[2].3)

1-Wire Receive Buffer Full*

IM3 (IMR.3);

EOWMI (OWD[5].7)

ERBF (OWD[3].4)

RBF (OWD[2].4)

1-Wire Receive Shift Register Full*

IM3 (IMR.3);

EOWMI (OWD[5].7)

ERSF (OWD[3].5)

RSRF (OWD[2].5)

1-Wire Short*

IM3 (IMR.3);

EOWMI (OWD[5].7)

EOWSH (OWD[3].6)

OW_SHORT (OWD[2].6)

1-Wire Low*

IM3 (IMR.3);

EOWMI (OWD[5].7)

EOWL (OWL[3].7)

OW_LOW (OWD[2].7)

* External Interrupts 10, external interrupt 11, and 1-Wire are only available on the 68-pin (RAX) version of the MAXQ2000.

Note 1: For 1-Wire Master interrupts to be received, both IM3 and EOWMI must be set to 1.

Note 2: The notation OWD[n] refers to accessing the OWD register with the OWA register set to n.

Maxim Integrated

15