Closed-loop stability, +5 vdc / +3.3 vdc power sequencing, Voltage hold-up time – Intel ATX12V User Manual

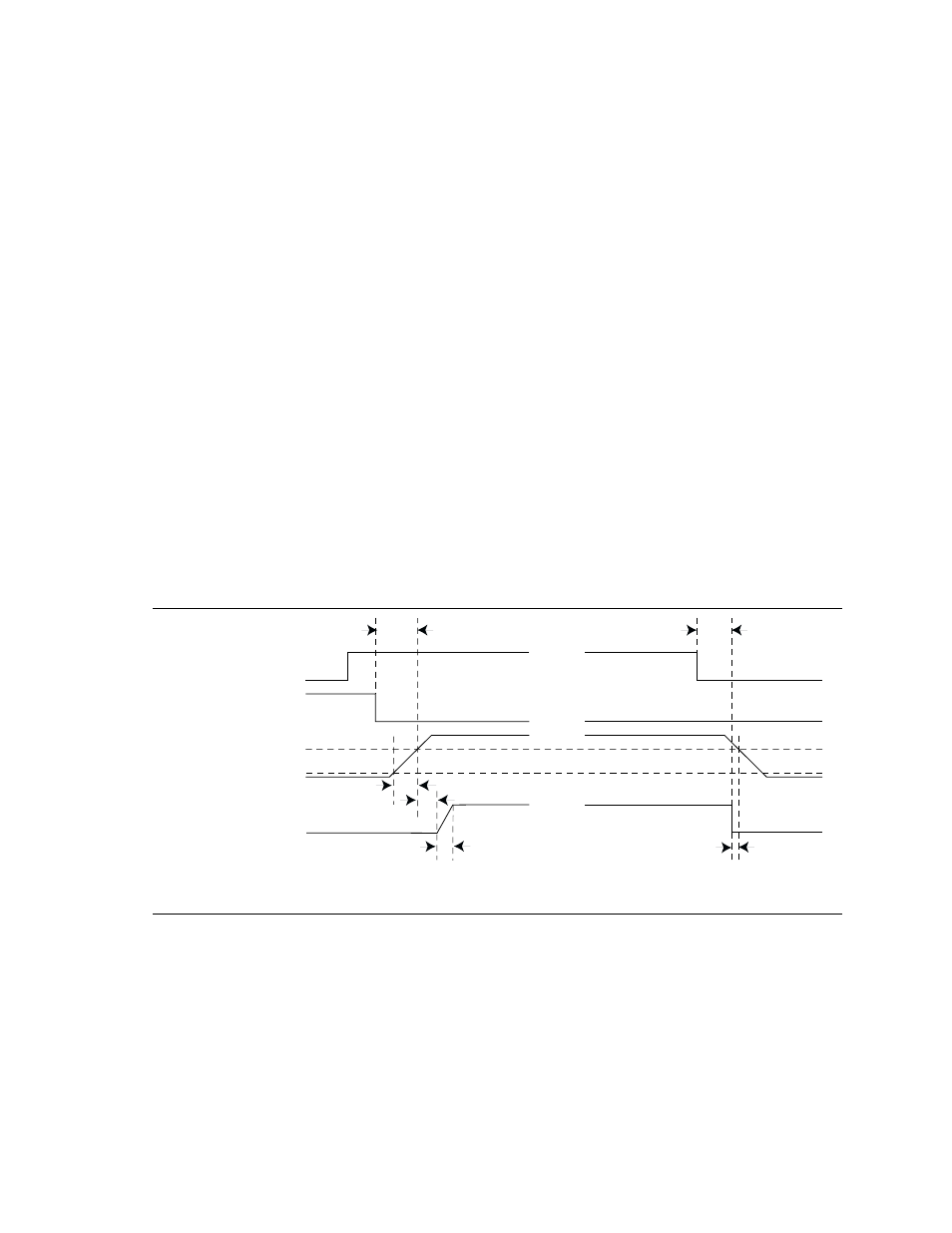

Page 22: Timing / housekeeping / control, Figure 6. power supply timing

ATX12V Power Supply Design Guide

Version 2.0

22

3.2.9. Closed-loop Stability

The power supply shall be unconditionally stable under all line/load/transient load

conditions including capacitive loads specified in Section 3.2.8. A minimum of 45 degrees

phase margin and 10 dB gain margin is recommended at both the maximum and minimum

loads.

3.2.10. +5 VDC / +3.3 VDC Power Sequencing

The +12 VDC and +5 VDC output levels must be equal to or greater than the +3.3 VDC

output at all times during power-up and normal operation. The time between the +12 VDC

or +5 VDC output reaching its minimum in-regulation level and +3.3 VDC reaching its

minimum in-regulation level must be

≤ 20 ms.

3.2.11. Voltage Hold-up Time

The power supply should maintain output regulation per Section 3.2.1 despite a loss of

input power at the low-end nominal range—115 VAC / 57 Hz or 230 VAC / 47 Hz—at

maximum continuous output load as applicable for a minimum of 17 ms.

3.3. Timing / Housekeeping / Control

PS_ON#

PWR_OK

PWR_OK Sense Level = 95% of nominal

95%

10%

~

~

~

T2

T3

T4

T6

timing_3_5_12b

+12VDC

+5VDC

+3.3VDC

O/P's

}

VAC

~

T5

T1

Figure 6. Power Supply Timing

Notes: T1 is defined in Section 3.3.4. T2 is defined in Section 3.3.5. T3, T4, T5, and T6 are defined in Table 13