Overview, Traditional" mode fifo mode – Integration 2.0r User Manual

Page 7

OVERVIEW

3

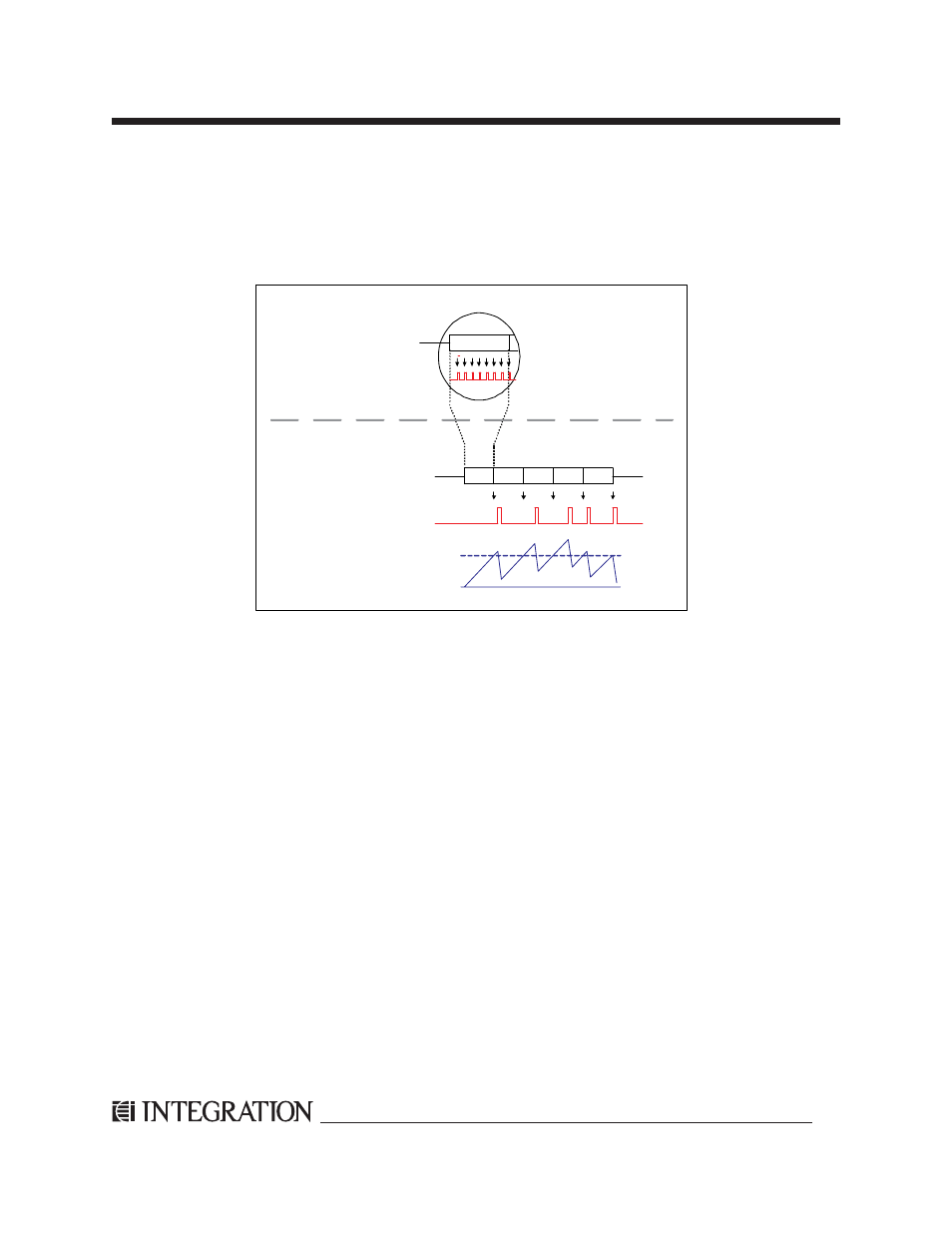

The demo uses the developer-friendly features of the IA4420 device. In receive mode the microcontroller reads the received

bytes from the IA4420’s FIFO, and transmits them through the TX latch. This approach dramatically reduces the load on the

micro, because the microcontroller doesn’t have to monitor every bit, only the bytes. This means the timing constraints in

an application can be reduced at least by a factor of eight for both the transmitting and the receiving sides. See the

PROCESSOR ACTIVITY lines on Figure 2, as demonstrated for both the ‘Traditional’ transceiver mode and the Integration

‘FIFO’ mode.

Fig 2. Process Activity in FIFO Mode when Compared to a Traditional Mode of Operation

RF PACKETS (8bit)

INTERRUPT REQs

PROCESSOR ACTIVITY

FIFO IT level

set to 8 bit

FIFO LEVEL STATUS

FIFO empty

1

3

2

5

4

byte1

DATA CLK

PROCESSOR ACTIVITY

"Traditional"

mode

FIFO mode